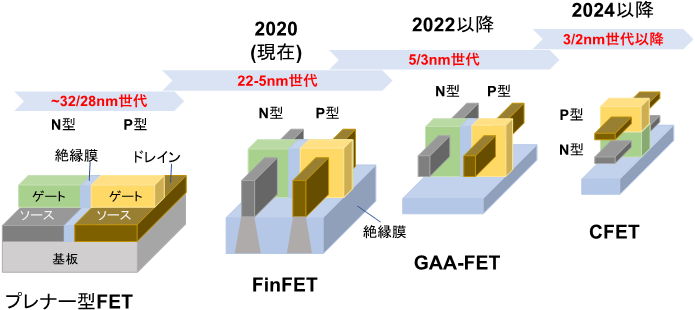

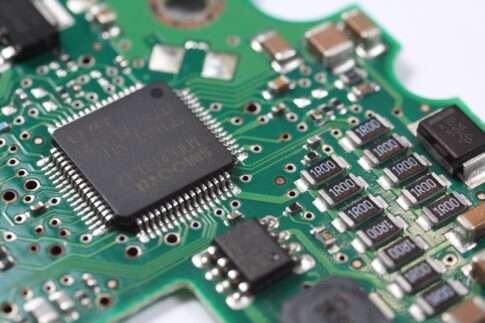

前回FET型のトランジスタについて書きましたので、今回はその中のMOSFETの構造変化について書いてみます。

時代とともに半導体の微細化が進むにつれて、MOSFETの構造も改良されてきました。

プレーナー型

最初に登場したのはプレーナー型というもので、ゲート部分が平坦な二次元平面上に配置されている構造です。日本ではこの構造が一番よく使われています。

半導体の微細化にあたってはMOSFETのサイズを小さくする、そのためにはゲート長を短くする、という方向で改良が進められてきました。そのため半導体の微細化を表すプロセスノードは以前はゲート長に則した値になっていました。

しかしプレーナー型トランジスタは22nmプロセスで限界になりました。

微細化によってソース-ドレイン間が狭くなったことで、しきい値電圧以下でもソースからドレインへ電子が移動するようになったり、ゲート絶縁膜も薄くなったことでゲート側への電子の侵入も生じるようになってしまったのです。

このようなリーク電流があるとトランジスタとして機能しなくなってしまいます。

そこで22nm以下の微細化に対応するため、従来のプレーナー型に続いてFinFETが登場しました。

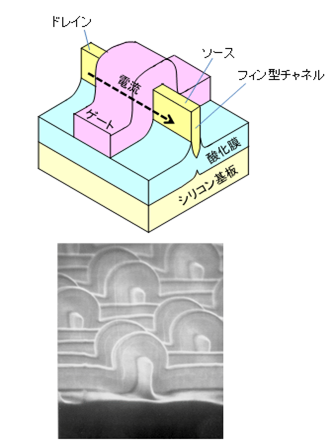

FinFET

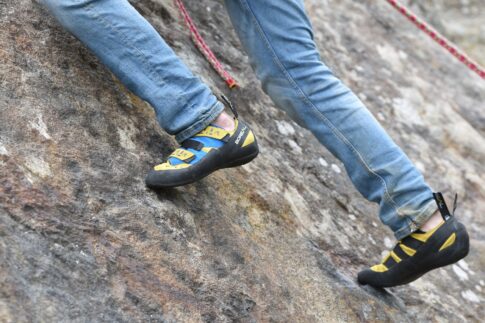

FinFETは1989年に日立製作所で開発されて1998年に特許2768719号で特許を受け、2011年にIntelの22nmプロセスで初めて量産化されました。Fin(魚のヒレ)形の三次元構造が特徴的です。

プレーナ型では微小化した際にゲート側にできる空乏層が不十分なためにリーク電流が生じるという点が課題となっていたため、FinFETではFin(ソース/ドレイン)部分の突起に絶縁膜とゲートを側面と上面の3方向から取り囲む構造にして、リーク電流を抑えることができるようになりました。

さらに3方向から取り囲む構造にしたことによりチャネル面積は大きくなり、ゲート長を極端に短くせずともFinの高さや幅を変えることによって高性能化を実現できるようになりました。

このようなことからFinFETが登場して以降はゲート長をプロセスノードの指標とすることは適さなくなりました。

10nm、7nm、5nmなどと呼ばれているものは、メーカー各社がそれ相当の集積度であるということをアピールするもので実際の寸法とは異なります。

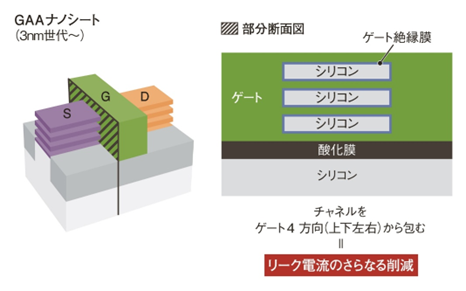

GAA

FinFETの発明と同時期の1988年に東芝で開発されたのがGAA型です。こちらは1998年に特許3057661号として特許を受けていますが、量産化はまだ始まったばかりです。

サムスン電子が2022年にGAA構造の3nm世代半導体の量産化にこぎつけました。

GAAはGate-All-Aroundの頭文字を取ったものですが、名前の通りチャネルの周囲の4面が全てゲートで覆われた構造になっており、より細かい電流制御や高い電力効果が実現できます。

CFET

GAAのさらにその先のトランジスタとして、2030年以降の1nm以下のプロセスノードでの採用が考えられているのがCFET型です。

GAA型ではP型半導体とN型半導体が横並びになっていましたが、CFETはこれを垂直方向に積み上げた構造になっています。このため平面積を大幅に削減することができ、配線長の短縮等によりさらなる性能の向上が期待されます。

複雑な三次元構造を作るための材料や製造技術が課題となります。

特許に関しては石村国際知的財産事務所のHPを参考にさせていただきました。

FinFETもGAAも日本人が最初に開発しているのに量産化の面では他国に後れを取ってしまったのですね。

このあたりの技術的な課題も特許明細書を読みながら勉強していきたいと思います。

7/1(月)学習時間:6.25H

・岡野の化学(147)続き~(148)

・EUVでレンズを使わない理由について

・SI基本単位の定義の変遷について(長さ、時間)

課題)

・SI基本単位がどのように決められてきたかは一通り調べておきたいので長さ・時間の他のものも調べる

その他

・3134 物事は直線的にとらえると失敗する

コメントを残す