半導体パッケージングの分野では、アンダーフィル技術がIC実装の歩留まりや信頼性を左右する重要要素となっています。

前回の記事ではアンダーフィルの基本について解説しましたが、今回はIBM社の特許 US11404379B2 を題材に、より実践的な改良技術を紹介します。

この特許は、Non-Conductive Film(NCF)アンダーフィルと、融点の異なるはんだを用いるsolder hierarchy(はんだ階層)とを組み合わせて、ブリッジチップとICチップの接合におけるずれ・酸化・はんだブリッジなどの不良を低減し、結果としてパッケージの信頼性と製造歩留まりを大幅に改善する技術を提案しています。

目次

発明の背景

まず、この特許が生まれた背景を説明します。

高密度配線の需要とブリッジチップ

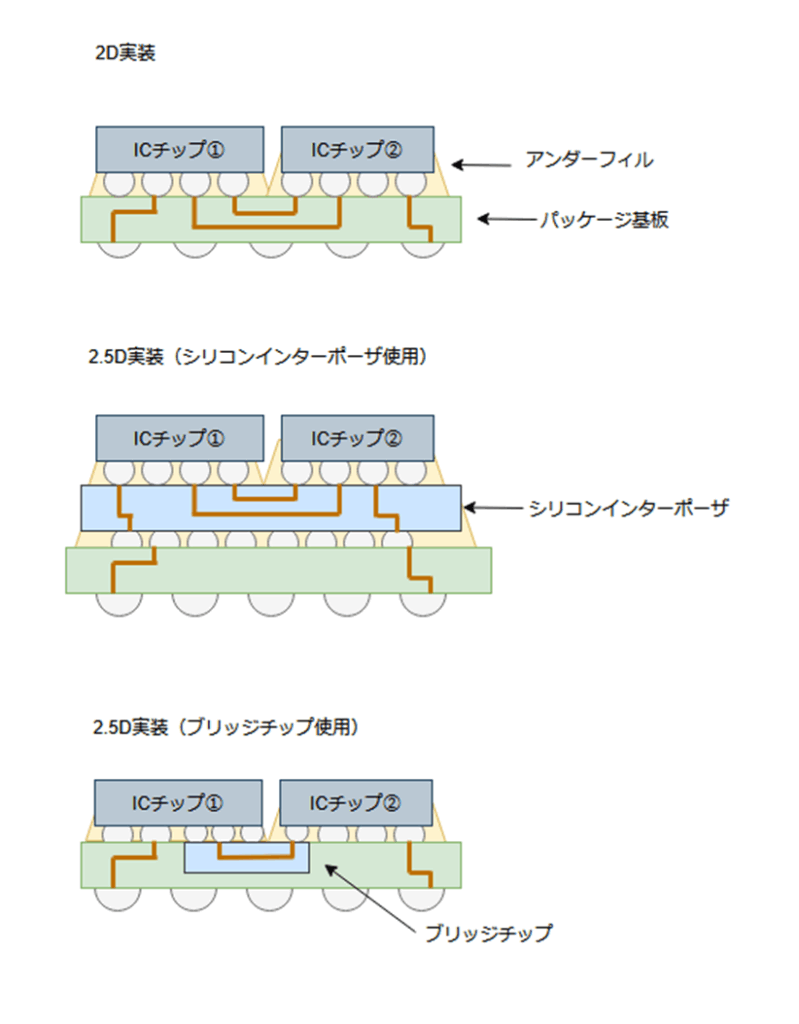

前回記事で説明したように、近年のICパッケージでは、複数のICチップ(ダイ)を高密度に接続するニーズが高まっています。

チップ間を短距離で接続し、細かいピッチで多数のI/Oを並べることで、高速・大容量・低消費電力での接続が可能になります。

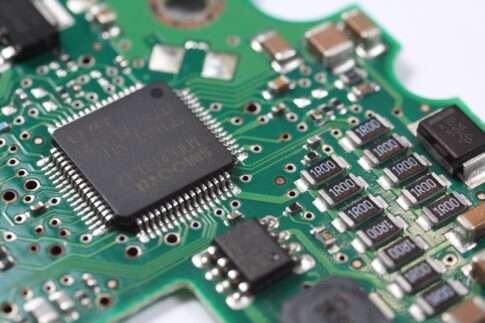

このような微細ピッチ・高密度配線を実現する代表的な技術がシリコンインターポーザです。

シリコン基板上に微細配線を形成することで、従来の有機基板では難しかったチップ間接続を可能にし、通信効率を大幅に高めました。

さらに、インテル社のEMIBに代表されるブリッジチップは、このシリコンインターポーザを改良した技術です。

高純度シリコンはコストが高いため、インターポーザ全体に用いるのは負担が大きいという課題がありました。

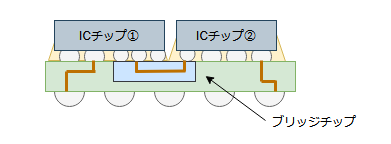

そこで必要な部分だけに微細配線を形成した短いシリコン片を埋め込み、複数のICチップ間の「橋渡し」をする方法が考案されました。これがブリッジチップです。

微細ピッチ・高密度配線の仕組みを車で隣町まで行く場合にたとえると、

- 道路の距離が短い → 信号が速く届く(高速)

- 道がたくさんあってたくさんの車が行き来できる → 一度に多くのデータを送れる(大容量)

- 短い距離を走るのでガソリンが少なくて済む → 駆動エネルギーが減る(低消費電力)

となります。

このように、高速・大容量・低消費電力で情報をやり取りできることにより、AI、5G、IoT、自動車などの先端分野で求められる高い処理能力を実現できます。

そして、このようなICパッケージを、熱、応力による歪み、衝撃などから保護し、信頼性を高めるための重要な実装技術が、前回紹介したアンダーフィルでした。

従来型のアンダーフィルとブリッジチップ接合の課題

しかし、従来のブリッジチップ接合やアンダーフィル工程には、製造コストや歩留まり、信頼性に関わる大きな課題が残されていました。

従来技術で使用されていたアンダーフィル技術は、キャピラリーアンダーフィル(capillary underfill:CUF)や非導電性ペースト(non conductive paste:NCP)でした。

CUFは、ICチップをブリッジチップ、あるいはパッケージ基板とはんだバンプで接合した後に、毛細管現象によって液状エポキシ樹脂を隙間に自然に行きわたらせ、その後熱で樹脂を硬化させるという方法です。

NCPは、接合前にチップにペースト状のアンダーフィル材を塗布してそれを押し広げながらブリッジチップ、あるいはパッケージ基板と接合し、はんだバンプを熱で溶融して接合させる工程で同時にアンダーフィルを硬化させるという方法です。

しかし、これらの方法では、アンダーフィル材に含まれるフィラーが小さなはんだバンプの隙間に噛み込まれてうまく塗り広げることができず、ボイドが発生するなど、均一な塗布が困難になっていました。

さらに、接合時のはんだの溶融順序にも課題がありました。

ブリッジチップでは、まずICチップとブリッジチップを接合してブリッジチップアセンブリを作り、次にそれをパッケージ基板に接合するという2段階のはんだ接合プロセスがありますが、この際、同じ材料からなるはんだバンプを利用すると、第2段階のはんだリフロー時に、最初に接合したはんだバンプが再溶融してしまうという問題がありました。

これにより、ICチップとブリッジチップとの間に位置ずれが生じ、接続信頼性や歩留まりに問題が生じていました。

発明の概要

上記のような課題を、本特許ではどのように解決したのか紹介します。

NCFを用いたブリッジチップ接合のプロセス

NCFを用いたブリッジチップ接合の工程は以下のようになります。

工程①:NCFの貼付

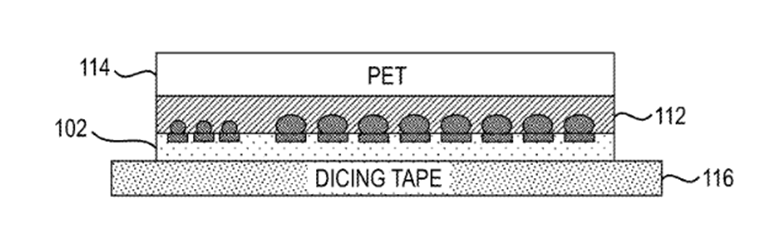

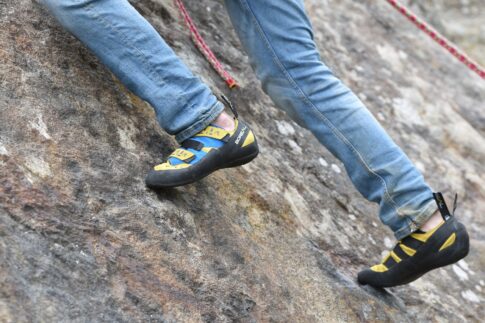

ICダイ(102)には、微細ピッチのはんだバンプ(ブリッジチップとの接合用)と、粗ピッチのはんだバンプ(パッケージ基板との接合用)の、2種類のはんだバンプが取り付けられています。

このICダイの表面に、NCF(112)を貼付します。そのままだと取り扱いが不便なので、NCFの表面にPET層を接着します。

原文にはICダイと書かれていますが、ウェハレベルでのNCFを想定していると思われるので、上図時点ではまだ個々のダイには分かれていません。

小さく切り分けた個々のダイにアンダーフィルフィルムを貼り付けるのではなく、ウェハ全体にアンダーフィルフィルムを貼付した後に、ウェハをダイシングテープで固定して、レーザ等で個々のダイに切り分けます。

ダイシング後、ダイシングテープとPETフィルムを剥離します。

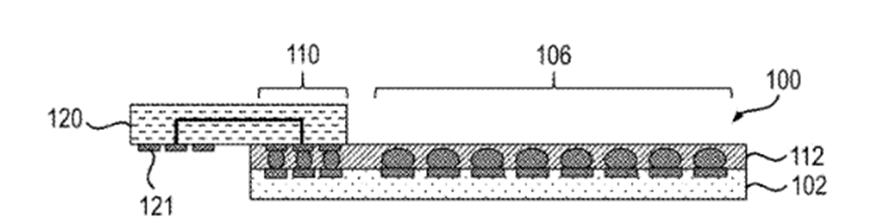

工程②:1つ目のICダイとブリッジチップの接合

接合には、フリップチップ接合でよく使われるサーモコンプレッションボンディング(Thermo-Compression Bonding:TCB)という方法が用いられます。

基板に熱と圧力を加えることではんだバンプを接合する方法です。

TCBは、ICダイを加熱したステージに載せ、ブリッジチップを位置合わせして、上から熱したボンディングヘッドで圧力をかけます。このとき、はんだバンプの高さよりアンダーフィルフィルムの厚みがやや大きくても、圧力によってはんだバンプがフィルムを突き破るので接合が可能になります。

工程③:2つ目のICダイとブリッジチップの接合

先ほど1つ目のICダイとブリッジチップを接合したので、同様のプロセスで2つ目のICダイとブリッジチップを接合します。

これにより、ブリッジチップが2つのICダイを橋渡しして、ブリッジチップアセンブリが形成されます。

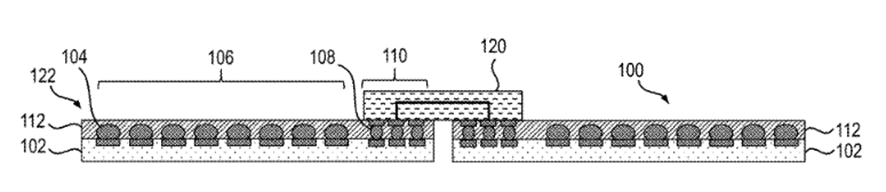

工程④:有機パッケージ基板への実装

ブリッジチップアセンブリ全体を有機パッケージ基板に実装します。

ここでは、ICチップの粗ピッチのはんだバンプがパッケージ基板に接合されます。

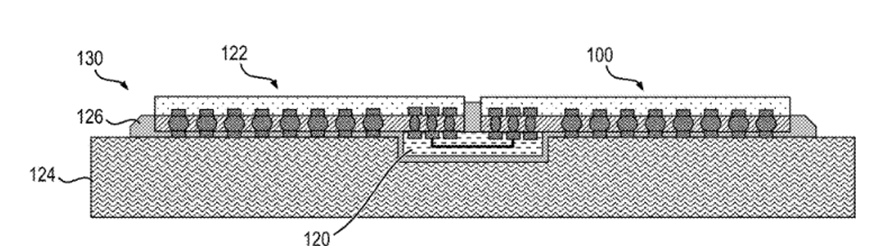

下図のように、パッケージ基板の一部にブリッジチップが埋め込まれた形になります。

特許の新規性

この特許の要は、非導電性フィルム(Non Conductive Film:NCF)とはんだ階層(solder hierarchy)を組み合わせて、ブリッジチップとICダイを安定的に接続するところにあります。

NCFでは、はんだ接合の前にICダイ表面にアンダーフィルフィルムを貼り付けてから、はんだバンプの接合を行うことにより、アンダーフィルの充填不足や不均一性といった課題を解消できるようになりました。

さらに、2段階の接合プロセスにおいて、最初に接合したはんだが再溶融してしまうという問題を、はんだ階層(solder hierarchy)によって解決しました。

これは、ICチップとブリッジチップとの接合部と、それらの基板との接合部において、それぞれ融点の異なるはんだバンプを使用するというものです。

例えば、上記の工程②③で、ICチップとブリッジチップとを接合する微細なはんだバンプには、高融点のはんだ材料を使用し、

工程④では、上記工程で形成されたブリッジチップアセンブリをパッケージ基板と接合する粗ピッチの大きめのはんだバンプには、低融点のはんだ材料を使用します。

融点の異なるはんだ材料を使用することにより、②③で先に接合したはんだは、④のより低温での工程では再溶融することがなく、接続の信頼性を確保できるようになります。

訳文検討

以下では、当該特許の原文から数カ所引用し、公開訳を参照しながら訳文を考えてみます。

私の訳文は試訳として載せています。

検討箇所①―ブリッジチップに関する説明

【原文】

The number of technology options continues to grow for advanced IC packaging, such as the introduction of silicon interposers or the shift towards modularization through multiple-chip module designs. Silicon interposers pose cost challenges as they are expensive and require a large silicon footprint, while multiple-chip module designs which use conventional packaging on organic substrates are limited by input/output (I/O) bandwidth and power efficiency.” An attempted solution to address the problems presented with silicon interposers and chip modularization has been the industry’s introduction of intermediary silicon dies—so-called silicon bridges—that connect two logic chips together (e.g., accelerator and high-bandwidth memory chips). These intermediary silicon dies are employed only in a limited scope, not using the same footprint as a full silicon interposer. One silicon bridge technology available from Intel Corporation, called Embedded Multi-die Interconnect Bridge (EMIB), makes use of a tiny piece of silicon with routing layers embedded in a common substrate that connects one chip to another in an IC package.

【公開訳】

シリコンインターポーザの導入またはマルチチップ型モジュール設計を通したモジュール化へのシフトなどの高度ICパッケージングについて、技術オプションの数は増え続けている。シリコンインターポーザは、高価であり、大きなシリコンフットプリントを要するのでコストについての課題をもたらし、有機基板上での従来式パッケージングを使用するマルチチップ型モジュール設計は、入出力(I/O)帯域幅および電力効率により制限される。シリコンインターポーザおよびチップモジュール化とともに提示される問題に対処するために試みられている解決法は、2つの論理チップ(例えば、アクセラレータチップおよび広帯域メモリチップ)を接続する中間シリコンダイ(いわゆるシリコンブリッジ)の業界による導入である。これらの中間シリコンダイは、限られた範囲のみで用いられ、シリコンインターポーザ全体と同じフットプリントは使用しない。インテルコーポレーションから入手可能な1つのシリコンブリッジ技術は、埋込み型マルチダイ相互接続ブリッジ(EMIB)と呼ばれ、ICパッケージ内で1つのチップを他のチップに接続する共通の基板に埋め込まれたルーティング層とともに小さなシリコン片を使用する。

【試訳】

シリコンインターポーザの導入やマルチチップモジュール設計によるモジュール化への移行など、先端ICパッケージングに関する技術選択肢の数は、増加し続けている。シリコンインターポーザは、高価であり、かつ大きなシリコンフットプリントを必要とするため、コスト上の課題をもたらす。一方で、有機基板において従来のパッケージングを使用するマルチチップモジュール設計は、入出力(I/O)帯域幅および電力効率によって制限される。シリコンインターポーザおよびチップのモジュール化に伴う課題に対処するために試みられた解決策は、2つのロジックチップ(例えば、アクセラレータおよび高帯域幅メモリチップ)を相互接続する中間シリコンダイ、いわゆるシリコンブリッジを業界が導入したことである。この中間シリコンダイは、全面にわたるシリコンインターポーザと同じフットプリントは使用せず、限られた範囲でのみ利用される。インテルコーポレーションから入手可能なシリコンブリッジ技術の一つで、埋め込みマルチダイ相互接続ブリッジ(Embedded Multi-die Interconnect Bridge:EMIB)と呼ばれる技術は、ICパッケージ内で一方のチップを他方のチップに接続する、共通基板に埋め込まれた、配線層を有する小さなシリコン片を使用する。

フットプリント(footprint)は、ここでは専有面積の意味で使われており、全面に使われていたシリコンインターポーザと、チップ同士を接続するわずかな範囲にのみシリコン片を用いるブリッジチップとが、a full silicon interposerとsilicon dies are employed only in a limited scopeという対比で説明されています。

そのため、ここでの full は、全体、全面といった意味になると思われます。どう訳すかは迷いましたが、試訳では「全面にわたるシリコンインターポーザ」としました。

引用箇所の最終文にある以下の箇所について、公開訳の解釈が疑問に思われました。

“a tiny piece of silicon with routing layers embedded in a common substrate that connects one chip to another in an IC package”

公開訳の解釈だと、that connects one chip to another in an IC packageの部分はa common substrateにかかり、embedded in a common substrateはrouting layersにかかっているようになっています。さらに、a tiny piece of silicon とrouting layersは別個にあって、その両方を使うというように読み取れます。

しかし、冒頭で説明したようにブリッジチップというのは以下のような構成になっています。

a tiny piece of siliconは、水色で描いたシリコン片のことですが、routing layersはそのシリコン片に形成された配線層のことを指していると思われます。したがって、routing layers とともにa tiny piece of siliconを使用するのではなく、routing layersを有するa tiny piece of siliconと解釈すべきかと思われます。

また、a common substrateは、上図の緑色で描いたパッケージ基板を指していると思われますので、routing layersだけが単独でa common substrateに埋め込まれているわけではなく、a tiny piece of silicon with routing layers全体が埋め込まれているということだと思われます。

そして、パッケージ基板の中に形成された配線で複数のICチップを接続していた2D実装とは異なり、ブリッジチップが複数のICチップを接続しているという文脈ですので、that connects one chip to another in an IC packageについても、a common substrateにかかるのではなく、a tiny piece of silicon with routing layersにかかっていると考えるべきかと思われます。

よって、試訳では、「ICパッケージ内で一方のチップを他方のチップに接続する、共通基板に埋め込まれた、配線層を有する小さなシリコン片を使用する」としました。

検討箇所②―従来のアンダーフィルの課題に関する箇所

【原文】

In conventional IC packaging methodologies, thermo-compression bonding (TCB) of copper pillar flip-chips with non-conductive paste (NCP) as pre-applied underfill is one of the solutions for bonding thin fine-pitch flip-chip devices onto organic substrates having a die thickness of greater than about 60 μm. However, this bonding process involves NCP spreading and curing together with solder wetting and joint formation processes. Several vital failure modes, such as NCP filler entrapment, NCP voiding issues, cracking and solder non-wetting, among other problems, may occur if process parameters and bonding profiles are not carefully optimized.

【公開訳】

従来式のICパッケージング方法体系では、非導電性ペースト(NCP)を予め塗布されたアンダーフィルとして用いた、銅ピラーフリップチップの熱圧着ボンディング(TCB)が、薄いファインピッチフリップチップ素子を、約60μmを超えるダイ厚さを有する有機基板に接合するための解決策の1つである。しかし、この接合プロセスは、はんだ濡れおよびジョイント形成のプロセスとともに、NCPを広げ、硬化させることを含む。数ある問題の中でもとりわけ、NCP充填剤の閉じ込め、NCPボイド化の問題、ひび割れ、および、はんだ濡れ不良など、いくつかの極めて重要な故障モードが、プロセスパラメータおよび接合プロファイルが注意深く最適化されない場合には起こり得る。

【試訳】

従来のICパッケージング手法では、先塗布型アンダーフィルとして非導電性ペースト(NCP)を用いた銅ピラーフリップチップのサーモコンプレッションボンディング(TCB)が、約60μm超のダイ厚さを有する有機基板に薄型狭ピッチフリップチップデバイスを接合するための解決手段の1つである。しかし、この接合プロセスには、はんだのぬれおよび接合形成プロセスとともに、NCPを押し広げ、かつ硬化させることが含まれる。プロセスパラメータおよび接合プロファイルが慎重に最適化されていない場合、数ある問題の中でも特に、いくつかの重大な不良モード、例えば、NCPフィラーの噛み込み、NCPボイド発生の問題、クラック、およびはんだぬれ不良が発生する恐れがある。

“bonding thin fine-pitch flip-chip devices onto organic substrates having a die thickness of greater than about 60 μm” の部分は、原文の表現が気になりました。

文構造上は、having以下はorganic substratesを修飾していると読むことになりますが、パッケージ基板を指していると思われる organic substrates に対して a die thickness という言い方をするのは不自然に思われますので、本来は、having 以下は、 thin fine-pitch flip-chip devices を修飾するように、”thin fine-pitch flip-chip devices having a die thickness…” と書きたかったのではないかと推測します。

試訳は原文の記載通り having 以下を organic substrates にかかるようにしましたが、コメントをすべきところかと思います。

“solder wetting and joint formation processes” は、はんだバンプによってICチップとブリッジチップを接合するプロセスを説明しています。

前回記事でも説明したように、このはんだ接合プロセスと同時に、アンダーフィル材を接合面全体に押し広げて硬化する(NCP spreading and curing)プロセスが行われるというのが先塗布型のアンダーフィルの特徴です。CUFでは、はんだ接合後に後から隙間にアンダーフィル材を導入するのとは対照的な方法です。

spreadには自動詞も他動詞もありますが、NCPはCUFのように自発的にアンダーフィル材が濡れ広がっていくというわけではないので他動詞で訳すべきところかと思います。

最終文では、NCPを適切に均一に充填するには、材料の濡れ性や、フィラーの含有量、加熱時の温度など様々な要素を適切に設計する必要があり、それができていない場合には色々な不良が生じてしまうということが説明されています。

filler entrapmentとは、アンダーフィル材の熱膨張率を下げたり流動性を増したりする目的で入れられるシリカ等のフィラーが、微細なはんだバンプ同士の隙間に詰まってしまい、均一な充填ができなくなるということを意味していると思われます。

NCP関連の資料を色々読んだところ、このような事象は「フィラーの噛み込み」と表現されているようなので、試訳ではこれを採用しました。

failure modeは、場合によって「故障モード」と「不良モード」のどちらも考えられますが、完成したデバイスの不具合は「故障モード」、実装工程など製造時の不具合「不良モード」という使い分けがされていることが多いようなので、今回は「不良モード」と訳しました。

検討箇所③―本特許の利点を説明する箇所

【原文】

By way of example only and without limitation, one or more embodiments may provide one or more of the following advantages:

use of a non-conductive underfill film on the surface of the IC dies or on the surface of the bridge chip prior to joining the bridge chip to the IC dies essentially eliminates the need for capillary underfill or non-conductive paste underfill, thereby avoiding filler entrapment and/or crack formation during bridge chip joining;

use of a solder hierarchy in the bridge chip assembly components prevents large solder bumps from melting during joining of the bridge chip to the IC dies, thereby reducing the occurrence of oxidation, movement/misalignment and/or bridging;

use of a solder hierarchy in the bridge chip assembly components prevents bridge chip interconnects from melting during subsequent bonding of the bridge chip assembly to an organic substrate; …

【公開訳】

限定することなく例としてのみ示すと、1つまたは複数の実施形態が、以下の利点のうちの1つまたは複数をもたらすことができる。

・ICダイにブリッジチップを結合する前に、ICダイの表面上、または、ブリッジチップの表面上で非導電性アンダーフィル膜を使用することで、キャピラリアンダーフィルまたは非導電性ペーストアンダーフィルの必要性が事実上なくなり、これにより、ブリッジチップ結合中の充填剤の閉じ込めおよび/またはひびの形成が避けられる。

・ブリッジチップアセンブリコンポーネント内ではんだの階層構造を使用することにより、ICダイへのブリッジチップの結合中に大きなはんだバンプが溶融することが阻止され、これにより、酸化、移動/不良位置合わせ、および/または、ブリッジングの発生が減る。

・ブリッジチップアセンブリコンポーネント内ではんだの階層構造を使用することにより、後に続くブリッジチップアセンブリの有機基板への接合中にブリッジチップ相互接続が溶融することが阻止される。

【試訳】

単に例示の目的であって限定するものではないが、1つ以上の実施形態は、以下の1つ以上の利点を提供することができる。

・ブリッジチップをICダイに接合する前に、ICダイの表面またはブリッジチップの表面に非導電性アンダーフィルフィルムを使用することにより、キャピラリーアンダーフィルまたは非導電性ペーストアンダーフィルの必要性が事実上なくなり、それによって、ブリッジチップ接合中のフィラーの噛み込みおよび/またはクラックの形成が回避される。

・ブリッジチップアセンブリ構成要素においてはんだ階層を使用することにより、ブリッジチップをICダイに接合する間に大型のはんだバンプが溶融することが阻止され、それによって、酸化、ずれ/ミスアライメントおよび/またはブリッジ形成が低減される。

・ブリッジチップアセンブリ構成要素においてはんだ階層を使用することにより、後に続くブリッジチップアセンブリの有機基板への接合中に、ブリッジチップの相互接続部が溶融することが阻止される。

movement は、misalignmentとスラッシュ記号で並べられていることから位置ずれを表していると思われますので、単に「移動」とするよりも「ずれ」の方が分かりやすいかと思いました。

crackは、「ひび」とするとやや一般的すぎるように思われるので、はんだ接合の文脈では「クラック」の方がよいのではないかと思います。

公開訳ではinterconnectsを「相互接続」としていますが、原文を読むとinterconnectsは溶融すると書かれているので、「相互接続」ではなく「相互接続部」とした方が、接続状態ではなく実態のある接続部であることが明確になるかと思われます。

コメントを残す