毛細管現象に関する前回記事に続き、今回は、半導体実装において毛細管現象を利用するCUPに代表されるアンダーフィル技術を取り上げます。

次回記事ではアンダーフィル関連の特許明細書を紹介する予定ですが、今回はその前提となる知識のまとめです。

アンダーフィル技術は、BGA(Ball Grid Array)やフリップチップ実装において、半導体チップと基板の間にエポキシ樹脂などの封止材を充填し、はんだ接合部を保護・補強する封止技術です。特に、スマートフォンや車載機器など、小型化・高性能化が進むポータブル電子機器において、この技術なしには製品の信頼性を保証することができません。

本記事では、アンダーフィル材が重要になっている背景、CUF、NUF、NCF、WLUFといった各種アンダーフィル方式の特徴、材料構成(エポキシ樹脂/シリカフィラー/硬化剤など)、および信頼性評価試験までを体系的に整理します。

目次

半導体デバイス分野における実装技術の意味とその変革の背景

今回の記事では、半導体デバイスの実装技術におけるアンダーフィルを中心に解説しますが、まずは前提として、半導体デバイス分野における「実装」の位置づけとその意味、実装技術が変化を遂げてきた背景について説明します。

「実装」の2つの意味

半導体デバイス分野で「実装」という場合、大きく次の2つの意味があります。

①パッケージングの意味での実装

②プリント基板への実装

パッケージングとしての実装

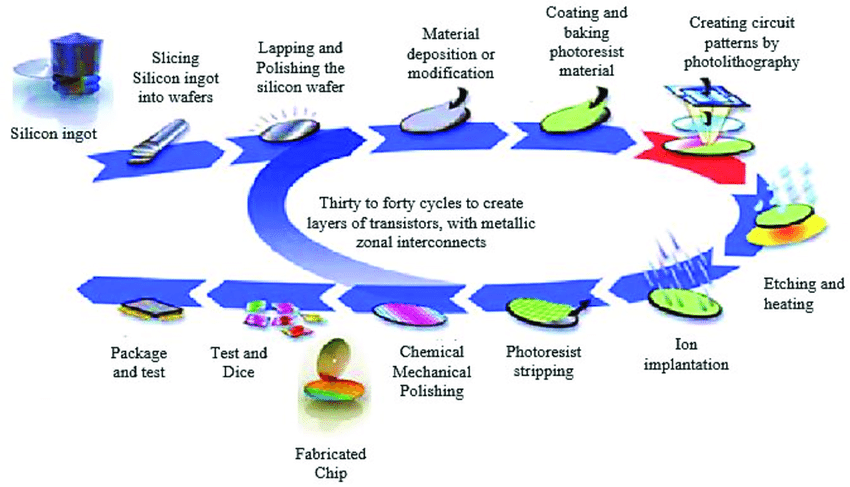

半導体の製造プロセスは、大きく前工程と後工程に分かれます。

前工程: ウェハ上に電子回路を形成する工程。下記を複数回繰り返す。

- 洗浄

- 成膜

- リソグラフィ

- エッチング

- イオン注入

- 平坦化

後工程: 電子回路が形成されたウェハをチップ化し、外部と接続できる形に仕上げる工程。

- ダイシング(チップ切り出し)

- チップ実装(接合:ワイヤボンディングやC4など)

- パッケージング(封止、外部端子形成)

- 動作テスト(パッケージテスト)

パッケージングとしての実装は、この後工程の中核であり、ウェハから切り出したチップを外部と安全かつ確実に接続できる形態に仕上げる重要なステップです。

プリント基板への実装

上記の後工程が完了し、製品化された半導体デバイスは、次にプリント基板(PCB)に取り付けられます。

実装方法には以下の2種類があります。

- 表面実装:プリント基板表面にはんだ付けなどで固定する方法

- 挿入実装:リードをプリント基板の穴に通し、裏側からはんだ付けで固定する方法

これらの方法で回路基板上に部品を取り付け、最終的に製品として動作可能な状態にします。

実装技術発展の背景

次の章で詳しく説明しますが、1970年代のDIP(Dual Inline Package)から現在まで、実装技術は多様な進化を遂げてきました。

その背景には、デジタルTV、携帯電話・スマートフォン、車載機器、IoTなど、多機能かつ高性能なポータブル機器の需要があります。

これらの機器では、

- 高機能でありながら軽量・小型・薄型化

- 過酷な環境(落下、衝撃、ほこり、高温など)での安定動作

が求められます。

こうしたニーズに応えるため、半導体実装技術では、デバイスの機能をできる限り小さい面積で最大限発揮できるように、多端子化・低背化・高密度化が進んでいきました。

多端子化が必要な理由は、外部との接続経路を増やすことで、より多くの信号や電力を同時にやり取りできるからです。

端子とそこにつながる配線をインターチェンジと高速道路、データを車に例えるとわかりやすいでしょう。道路の本数が多ければ、多くの車を同時に運べるように、端子数を増加することで、大量のデータを同時に処理することができます。

また、高性能チップでは安定した電源供給やノイズ低減のために電源端子やグラウンド端子も複数必要となります。

実装技術の変遷

続いて、実装技術がどのように変化してきたのか、先ほどの2つの実装の観点から詳しく見ていきましょう。

プリント基板への実装技術の変遷

まずは、半導体デバイスをプリント基板に実装する技術について、どのように変化してきたのかを見ていきましょう。

挿入実装から表面実装へ

1970年代後半から1990年代にかけては、ピンが周辺に配置されたパッケージが主流となっていました。このように端子がパッケージの周辺に配置されたタイプをペリフェラル型と呼びます。

ペリフェラル型パッケージの中での大きな転換点は、挿入実装から表面実装への変化です。

挿入実装タイプの例としては初期のDIP(Dual Inline Package)が挙げられます。

これは、長方形のパッケージの両長辺にピンが下向きに並んだタイプのパッケージです。

この下向きのリードを、プリント基板を貫通するようにあけられた穴(スルーホール)に挿入し、リードが長い場合はカットしたり折り曲げたりした後で、基板の裏側からはんだ付けします。

挿入実装タイプは、固定強度は優れていますが、基板の片面しか使えなくなるため設計の自由度が低く、また基板に穴をあける工程や、そこにピンを通す工程などは手間がかかります。また、リードが長くなることで寄生インダクタンスが増大するという問題もあります。

導体に電流が流れると、右ねじの法則に従ってその周囲に磁界が生じます。電流が変化すると磁界も変化しますが、この磁界の変化に対して、それを妨げる向きの起電力が発生します。電流変化に対するこの起電力の大きさを比例定数として表したものがインダクタンスです。

インダクタンスは意図的に設計することもありますが、リードフレームや配線パターンの長さ・形状によって、意図せず生じる場合があります。これを寄生インダクタンスと呼びます。

寄生インダクタンスは、電流が変化するとき、その変化に比例した起電力を生じます。これは上記の通り変化を打ち消す方向にはたらくため、信号の立ち上がり・立ち下がりを遅らせたり、波形を歪ませたりします。その結果、特に高速デジタル信号や高周波信号では、タイミングエラーや誤動作の原因となります。

導体が長いほど磁界が存在する領域も大きくなるため、寄生インダクタンスは導体の長さが長くなるほど大きくなります。電流変化が急峻な条件ほど、寄生インダクタンスの影響が顕著になります。

上記のような挿入実装タイプに代わり1980年代に登場したのがQFP(Quad Flat Package)に代表される表面実装タイプのパッケージです。

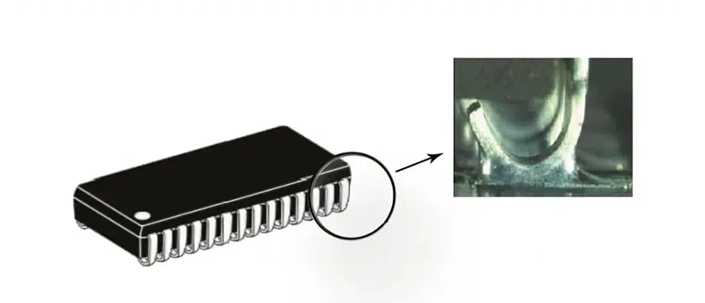

QFPは、パッケージの四側面からリードが伸びていて、そのリードがガルウィング形状(カモメが翼を広げたような形状)に成形されていることが特徴です。

あるいは、SOJ(Small Outline J-leaded package)のように、リードがJ字型に内側に折り曲げられているタイプもあります。

これらのタイプは、リードをプリント基板の表面に直接はんだ付けすることができるため、表面実装タイプと呼ばれます。

挿入実装タイプで問題となっていた工程の手間やリード長の問題を低減することができるため、以後の実装技術では表面実装が主流となりました。

しかし、上記のペリフェラル型の実装方法は、いずれも端子をパッケージの周囲にしか配置できないため、端子数を増やすにはパッケージを大きくして外周を伸ばすか、端子を細くして間隔を狭くするかしかありません。

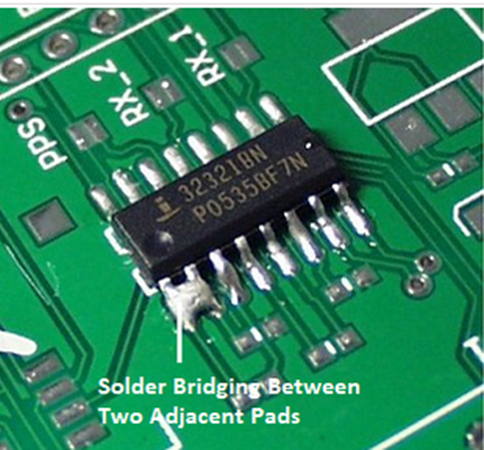

パッケージを大きくすれば専有面積が増えて小型化の流れに逆行しますし、端子間を狭くすると、本来つながってはいけないリード同士をつないでしまうはんだブリッジと呼ばれる接続不良が起きやすくなります。

つまり、ペリフェラル型には、構造的に端子数の増加と小型化の両立が難しいという課題がありました。

ペリフェラル型からエリアアレイ型へ

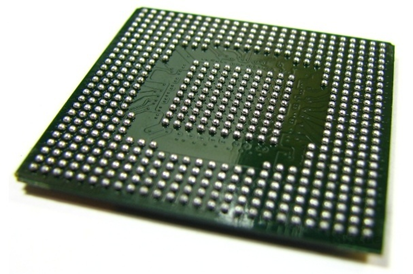

上記のペリフェラル型に変わって1990年代に登場したのが、BGA(Ball Grid Array)や、それをさらに小型化したFBGA(Fine Pitch BGA)、CSP(Chip Scale Package)など、パッケージ全面に端子を配置するエリアアレイ型です。

エリアアレイ型の多くは、これまでのリード型の端子に代わり、はんだボールと呼ばれる球状のはんだなどを利用します。

半導体チップの底面全体にはんだボールを並べたBGAでは、同じ面積のパッケージでも端子数を格段に増加することができ、パッケージの小型化が容易になります。

また、上述のように、ペリフェラル型のQFPでは多端子化・小型化のためにリードピッチを狭めるとはんだブリッジが起こりやすくなるといった問題がありますが、BGAでは比較的歩留りを高くすることができます。

また、はんだボールはリードに比べて高さが低く導体長が短いため、寄生インダクタンスを抑えられます。

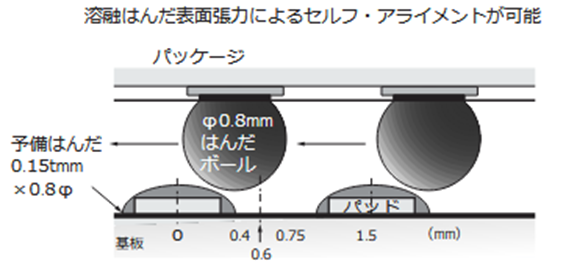

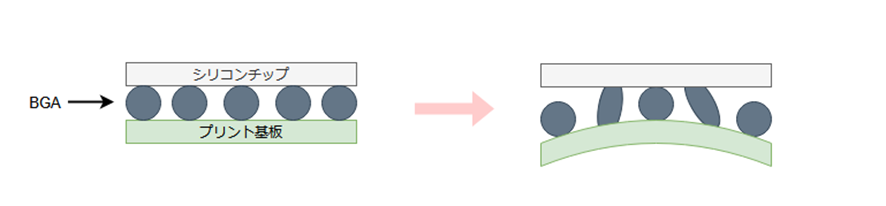

さらに、BGAを用いるうえでの大きなメリットは、はんだの表面張力によるセルフアライメントが可能になるということです。

前回記事に書いた通り、表面張力とは液体分子が表面を最小にするように働く力のことですが、2つの液体の玉があったとすると、その2つが合体した方が表面積を小さくできるため、2つの液体の玉が出会うと両者は合体します。

この原理を利用して、基板側にも予備はんだを設けておくことで、溶融時にBGAのはんだボールと予備はんだの間に表面張力がはたらき、仮にBGAがわずかにずれて配置されたとしても正しい位置に動いてくれるのです。

(画像引用元:萩本英二「パッケージから見た高速実装技術―CSPを中心に」Design Wave Magazine No.19、1999年1月号)

パッケージング技術の変遷

続いて、もう一つの「実装」であるパッケージングについて変遷を見ていきましょう。

パッケージ内部の接続方式も、上記のペリフェラル型からエリアアレイ型への変化に伴い、1980年代~90年代のワイヤボンディングから、C4接続法を用いたフリップチップ実装へとシフトしていきました。

ワイヤボンディング

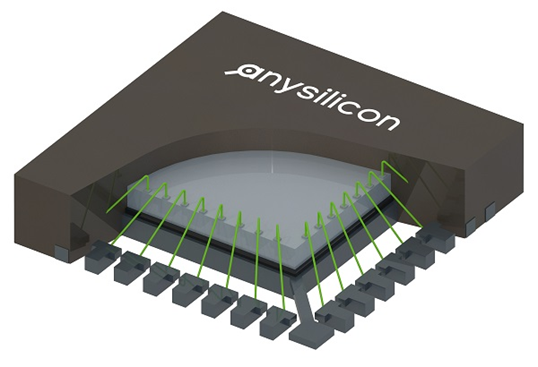

ワイヤボンディングは、金、銀、銅、アルミニウムなどの極細のワイヤ(15μm~500μm)を使って、半導体チップとパッケージ基板とを接続する方法です。

特殊な設備が不要で、比較的低コストで高密度な実装が可能です。

上図はワイヤボンディングしたチップを樹脂で封止してパッケージ化したものですが、パッケージを用いずに、チップを直接プリント基板にワイヤボンディングで取り付けるベアチップ実装という方法で使われることもあります。

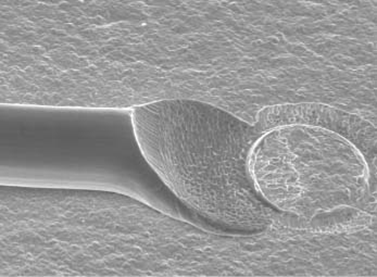

ワイヤボンディングにはボールボンディング方式とウェッジボンディング方式の2通りがありますが、主流となっているのはボールボンディングです。

ボールボンディングのプロセス:

① 1stボンド(チップ側接合)

・キャピラリと呼ばれる専用装置からワイヤを送り出し、スパークで先端を溶かしてボールを形成

・このボールを半導体素子の電極に押し付け、荷重と熱・超音波振動で接合

・ボール状になることで接合面積が大きくなり、信頼性が向上

② ループ形成

・弧を描くようにキャピラリを動かし、ワイヤループを形成

③ 2ndボンド(基板側接合)

・ワイヤを基板側の電極に押し付け、荷重と熱・超音波振動で接合

・この接合部はボール形状を作らないため、ステッチボンドと呼ばれる

④ 切断(テールカット)

・ワイヤを引き上げて切断し、1本のボンディングが完了

ワイヤボンディングは成熟した技術で、多くのパッケージで採用されていますが、構造上はチップ周囲に端子を配置するペリフェラル型が基本です。

そのため、配線長が長くなり寄生インダクタンスが増加しやすく、高周波特性や端子数増加に限界があります。

C4接続法

上記のような背景から、ワイヤボンディングに代わるより短距離で高密度な接続方式としてC4接続法によるフリップチップ実装が登場し、1990年代以降主流の一つとなっていきました。

C4接続法とは、Controlled Collapse Chip Connectionの頭文字を取って命名された方法で、バンプと言われるこぶ状のはんだ突起を介して半導体チップとパッケージ基板電極とを接続する方法です。

C4はチップとパッケージ基板(または後述するインターポーザ)の接続技術であり、BGAは完成したパッケージ外部の端子形態を指します。先に説明したBGAもC4接続法を応用した技術であり、同様にエリアアレイ型の接続が可能です。

フリップチップ実装とマルチチップの発展

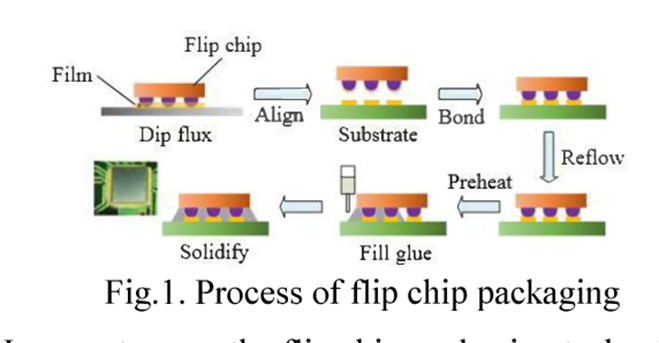

BGAと違ってパッケージにおけるC4接続法で特徴的なのは、フリップチップ実装との融合です。

フリップチップ実装とは、半導体チップの裏側にはんだバンプを載せておき、チップを180°反転(Flip Chip)させてパッケージ基板と接合させる方法です。

フリップチップは、マルチチップICと呼ばれる、複数のICチップを1つのパッケージに収納するパッケージ技術や、SiPと呼ばれる、異なる種類の機能ブロックを1つのパッケージにしてシステムとして動作できるようにした技術において非常にメリットがあります。

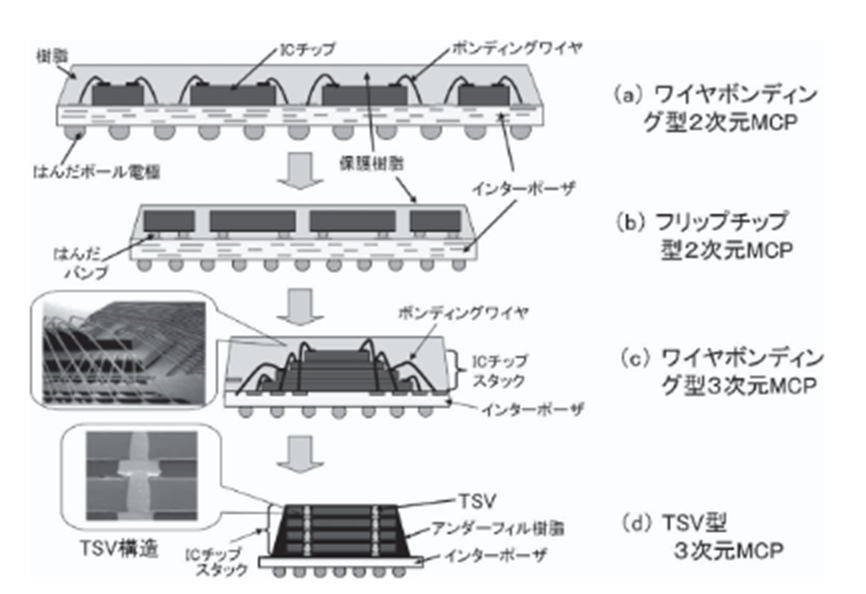

マルチチップ初期のワイヤボンディングを用いた2D実装と呼ばれる方式では、下図のように複数の半導体チップがワイヤボンディングで各々パッケージ基板に接続された状態で横並びに配置されるため、パッケージ全体が大型化してしまいますが、フリップチップを介した接続にすることで、同じチップを使用した2D実装でも小型化することができるようになりました。

(画像引用元:本多進「半導体素子の2D~3D実装技術動向と狙うべき方向」(エレクトロニクス実装学会誌、Vol.18、No.3、2015))

さらに、パッケージ基板への接続に代わり、インターポーザと呼ばれる中間層によって各チップを接続することで、チップ間をさらに短距離・多数の信号線で接続できるようになりました。

インターポーザは主にシリコンを使用するため、半導体の微細加工技術によってより細かく高密度な配線を形成できるのです。

横並び配置であっても、基板ではなくインターポーザで接続することで高密度・短距離の配線が可能となるため、これを2.5D実装と呼びます。

さて、これ以上の小面積化を実現するにはどうすればいいでしょうか?

これは少ない面積の土地にたくさんの人を住まわせるのと同じことで、横並びになっていた平屋建ての建物を高層ビル化すればよいわけです。

こうした発想から出てきたのが3D実装で、各チップ同士をフリップチップで接合したものや、積層したチップ全体を貫通するTSV(Through silicon via)と呼ばれる電極で接続する方法があります。

以上のように、プリント基板への実装とパッケージングの技術が相互に影響し合いながら、多端子化・小型化に対応した高性能な実装技術が進化してきました。

そして、この高密度・高信頼の接続を維持するために不可欠となるのが、次章で説明するアンダーフィル技術です。

アンダーフィルの役割と重要性

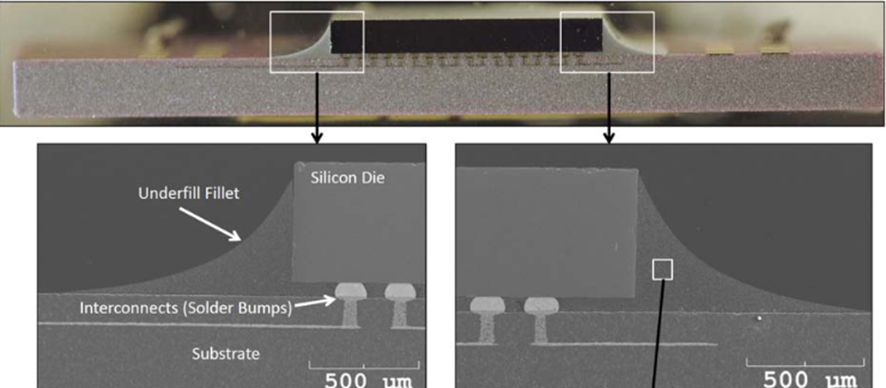

先に説明してきたように、BGAのようなはんだボールを用いたパッケージとプリント基板の接続、あるいはC4接続法によるフリップチップ接合におけるはんだバンプとパッケージ基板・インターポーザとの接続は、多端子化・小型化において欠かせない実装技術です。

これらの技術を実現するうえで重要となるのがアンダーフィルの存在です。

アンダーフィルがどのような役割を持つのかを、以下で紹介していきます。

熱膨張差による応力緩和

シリコンチップと有機基板では熱膨張率が大きく異なります。

シリコンチップの熱膨張率が約2.6ppm/℃であるのに対し、通常の配線基板であるガラス・エポキシ樹脂の熱膨張率は約12~16ppm/℃です。

ppmはparts per million の略で、100万分の1を表す単位です。

熱膨張率は一般に線膨張率として定義され、温度が1℃上昇するごとに元の長さに対してどれだけ伸びるかを示します。例えば、熱膨張率1ppm/℃は、温度が1℃上昇するごとに元の値の100万分の1だけ膨張することを意味します。

このような熱膨張率の差による応力がはんだ接合部に集中し、はんだの歪みやクラックにつながる恐れがあります。

アンダーフィルは、このような応力を樹脂で分散し、接合部の破壊を防ぐ役割をしています。

接合強度の向上

また、小型化・狭ピッチ化にともない、BGAをさらに小型化したFBGAで使用されるはんだボール、フリップチップ接合に用いられるはんだバンプは、その接合面の小ささゆえに機械的強度が限られます。

さらに、近年では環境への配慮から鉛を使わない鉛フリーはんだへの要求が高まっており、鉛入りのはんだに比べて融点が高く、延性が低く硬くてもろいはんだが使用されるケースも多くなっています。延性が低いということは、外力や熱膨張差に対して塑性変形で吸収できず、そのまま応力が集中してクラックが入りやすいということです。

アンダーフィルは、はんだ接合部を物理的に囲い込み、外力に対する耐性を向上させます。

熱的・物理的ダメージへの耐性

冒頭でも触れたように、携帯端末や車載用途などのポータブル機器では、落下や振動による瞬間的な衝撃や高温環境が生じます。

アンダーフィルは、高いガラス転移温度や低い熱膨張係数を持つよう設計されており、これらの熱的ダメージや衝撃を緩和し、接合部の信頼性を高めます。

これらの理由から、アンダーフィルは高密度実装の信頼性確保に欠かせない存在であり、次に説明する各種アンダーフィル方式の理解は、現代の半導体実装技術を語るうえで避けて通れません。

アンダーフィル方式の変遷

アンダーフィルの充填方法にはいくつかの種類があります。

ここでは代表的な、CUF、NUF、NCF、WLUFを紹介します。

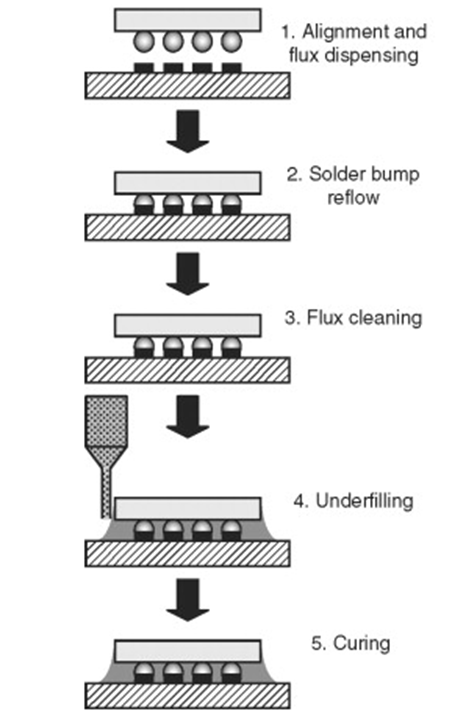

CUF(Capillary Underfill)

CUF(Capillary Underfill、キャピラリーアンダーフィル)は、前回記事で取り上げた毛細管現象を利用した充填方法です。

この方法では、実装後に硬化前のアンダーフィル材を端から供給すると、毛細管現象によりチップと基板の間のごく狭い空間にアンダーフィル材が自然に入り込んで接合部全体に充填されます。その後、加熱によりアンダーフィル材を硬化させます。

この方法はシンプルで汎用性が高く、後工程への影響も少ない一方で、充填時間が長いというデメリットがあります。

また、はんだバンプがさらに20μm未満の微細ピッチになると、アンダーフィル材の粘性による抵抗が大きくなり、十分にアンダーフィル材を行きわたらせることができなくなってしまいます。

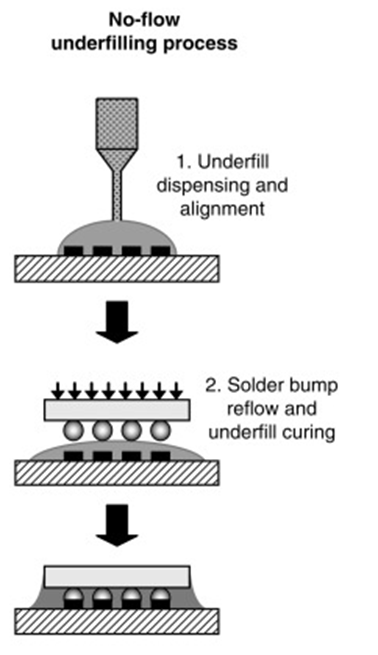

NUF(No-Flow Underfill)

NUF(No-Flow Underfill、ノーフローアンダーフィル)は、上記のCUPのように接合後にアンダーフィル材を流し込むのとは異なる方法です。

NUFでは、チップ実装前にアンダーフィル材を基板に塗布し、その上からチップを載せて、はんだの溶融接合(リフロー)時にアンダーフィル材も同時硬化させます。

NUFは、微細ピッチでも均一に樹脂が介在するため充填ムラやボイドのリスクが低く、生産性にも優れますが、はんだ接合と樹脂硬化が同時進行するため材料設計に制約があります。

特に、後述するように従来のアンダーフィルで広く使われるシリカフィラーは、NUFが使われる極微細ピッチでは、シリカフィラーの粒径が大きいと樹脂中での分散が不均一になり、充填時にバンプ間を塞いでしまう恐れがあります。

また、フィラーの含有量や粒径分布によっては樹脂の濡れ性や流動性が低下し、均一な充填が難しくなります。このためNUFでは粒径の小さいフィラーやフィラー無添加配合が選択されることもありますが、その場合は熱膨張率が高くなり、応力緩和性能がCUFより劣る傾向があります。

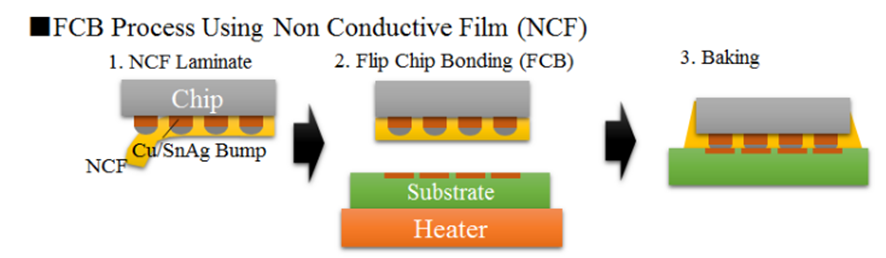

NCF(Non-Conductive Film)

NCF(Non-Conductive Film、非導電性フィルム)も先ほどのNUFと同様、チップ実装前にアンダーフィル材を塗布しておいて、はんだリフロー時に同時硬化させる方法です。

NUFと異なるのは、液体状のアンダーフィル材を塗布するのではなくフィルム状のアンダーフィル材をチップに先に貼り付けておき、それを基板に接合するという点です。

NCFや先ほどのNUFは、チップと基板の接合後にアンダーフィル材を充填するCUFに対して、先にアンダーフィル材を塗布しておくため、先塗布型と呼ばれます。

工程短縮や充填ムラを低減してより狭ピッチにも対応できるというメリットがありますが、NUFと同様に材料設計の自由度が限られ、接合条件の最適化が不可欠です。

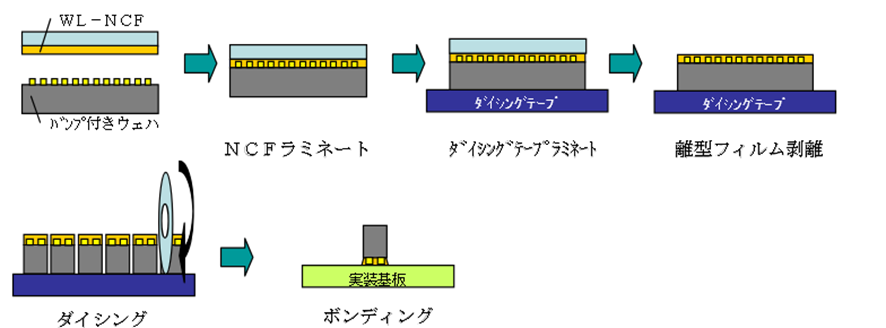

WLUF(Wafer-Level Underfill)

WLUF(Wafer-Level Underfill、ウェハレベルアンダーフィル)は、上記NCFをさらにウェハレベルに拡大してさらなる量産化と工程集約をねらった方法です。

半導体製造プロセスの後工程において半導体ウェハをダイシングする前に、ウェハ状態のままアンダーフィル材のフィルムを貼り付けておき、バンプ電極付きウェハと、あらかじめアンダーフィル材フィルムを貼り付けたウェハとを高精度位置合わせ装置でアライメントし、加熱・加圧して一括接合します。そして最後にこれをチップに切り分けます。

ウェハレベルで処理するためスループットが高く、個片状態での処理工程を省略できるため、極微細ピッチ実装でも歩留まりを確保しやすい方式です。

ただし、バンプ高さと樹脂層のバランスが不適切だとボイドや界面破壊の原因になるため、接着時の厚みの制御が重要です。

アンダーフィル材の主な材料と求められる特性

続いて、アンダーフィル材にはどのような素材が使われているのか見ていきましょう。

主な材料

アンダーフィル材は一般的に、エポキシ樹脂をベースに、シリカフィラーや硬化剤を組み合わせてできています。これにより機械的強度、熱特性、電気絶縁性を確保します。

エポキシ樹脂

アンダーフィル材のメイン材料となるのはエポキシ樹脂です。

エポキシ樹脂には、1分子中に下図のエポキシ基が2個以上含まれます。

エポキシ樹脂は、熱硬化性樹脂に分類されます。

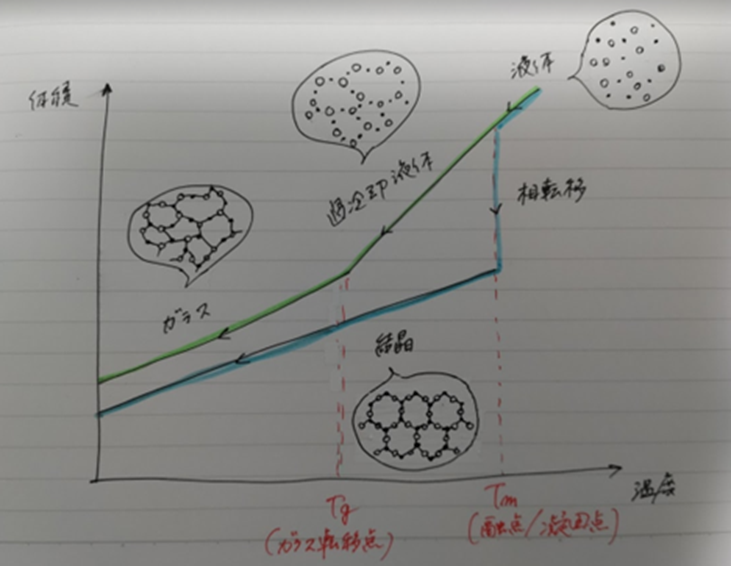

熱硬化性樹脂は加熱することで硬化し、一度硬化すると再び加熱しても元に戻りません。このような変化は不可逆性の変化と呼ばれます。

熱硬化性樹脂と対象的にポリエチレンなどは熱可塑性樹脂と呼ばれ、冷却させることで硬化しますが、加熱すると再度軟化します。こちらは可逆性の変化です。

料理で例えると、熱硬化性樹脂は玉子、熱可塑性樹脂はチョコレートのようなものです。

チョコレートは一度冷やして固めても再び加熱して溶かして成形することができますが、玉子は一度加熱して目玉焼きにしてしまったら再び元の状態に戻すことはできません。

このような熱硬化性樹脂は、硬化すると非常に強固になるため、微細な電子部品やチップと基板の接合部を外部の衝撃・振動などから保護するのに適しています。

さらに、エポキシ樹脂は、耐薬品性、耐水性、耐湿性、耐熱性にも優れ、硬化時の寸法収縮も少ないというメリットがあります。

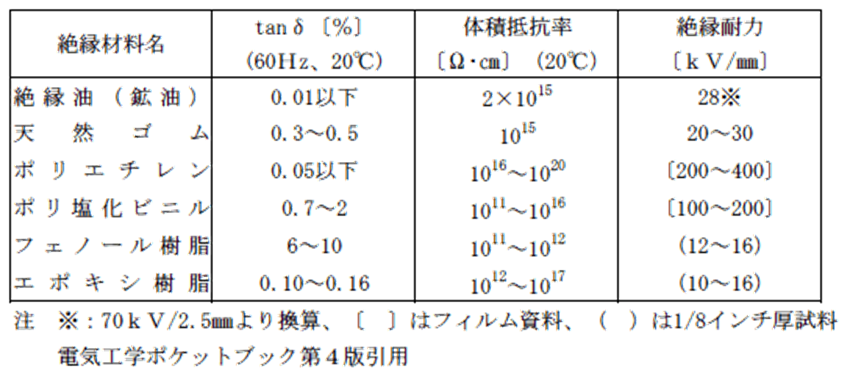

また、アンダーフィル材として欠かせない絶縁性にも優れています。

電気を通しやすい金属のような物質が導体、条件によって電気を通したり通さなかったりする物質が半導体、電気を通しにくい物質を絶縁体と呼び、エポキシ樹脂は絶縁体です。

電気の通しにくさ(絶縁性)を表す体積抵抗率は、1立方メートルあたりの物体について、互いに向かい合う2面間の内部を電気が流れる場合の抵抗値として、単位(Ω・m)あるいは(Ω・cm)で表されます。体積抵抗率が大きいほど電気を通しにくくなります。

ただし、絶縁体であっても、ある強度以上の電界が印加されると絶縁体の電気抵抗が急激に低下して急激に電流が流れるようになる絶縁破壊という現象が生じます。

例えば、空気は絶縁体ですが、雲の中の静電気が高電圧状態となり大地との電圧差が大きくなった場合に絶縁破壊が起きて落雷現象として現れます。

このように絶縁破壊の生じる電界強度を絶縁体の絶縁耐力といいます。

絶縁耐力は材料の厚さや気泡の有無、フィラーの分散状態に大きく影響を受けるため、アンダーフィル材の浸透具合や組成を十分に考慮する必要があります。

ポリウレタン樹脂

エポキシ樹脂は上記のメリットがありますが、硬化後のアンダーフィルは除去が難しいため、不良が生じた際にその部分だけ直すということが難しく、不良パッケージ全体を取り換えする必要が出るという点でコストがかかります。

したがって、リペア可能性と信頼性のバランスを保ったアンダーフィル材への需要も増しています。

このようなリペア性の観点からベースとして使用されるものにはポリウレタン樹脂があります。

ポリウレタン樹脂は、加工成形しやすく、柔軟で衝撃に強いというメリットがあります。

ポリウレタン樹脂には熱硬化性と熱可塑性の両方がありますが、熱可塑性ポリウレタン樹脂を使用することでリペア性にも優れるため、不良部品を回収・修理して使用することができます。

ただし、エポキシ樹脂に比べると耐水性、耐熱性、絶縁性は劣ります。また高温環境下では熱膨張率が大きくなります。

シリカフィラー

アンダーフィル材の熱膨張率が高いと、先に書いたような応力に起因するはんだの歪みを生じさせてしまうため、熱膨張率を下げる必要があります。

このため、樹脂中に無機フィラー、例えばシリカ(SiO2)粒子などを分散させるという対策がとられています。

アンダーフィル材には多くの場合、球状のシリカ粒子が用いられています。

球状シリカには、

・表面がシリカ層で覆われていて内部が空洞になっているタイプ、

・微細な一次粒子がさらに凝集してできた二次粒子が細孔を持ちながら球状にまとまっているシリカゲルのようなタイプ、

・内部が詰まっていて細孔のないタイプ、

があります。

アンダーフィル材に使用される球状シリカ粒子は3番目のタイプで、主に溶融法という方法で作成されます。

溶融法は、粉砕した原料シリカを高温の火炎中で溶融し、表面張力によって球状化させ、急激に冷却します。

冷却というのがポイントで、通常は溶融状態のシリカをゆっくりと冷却させていくと徐々に分子が整列して結晶となりますが、急冷することにより分子がきちんと整列しないまま固化するため、非晶質(アモルファス)と呼ばれる状態になります。

喩えで言うと、休み時間にグラウンドを走りまわっている生徒に「止まって!」と急に声をかけると、その場でバラバラの位置関係で動きを止めます。きちんと整列してもらうには、時間をかけて並び終わるのを待たないといけません。

分子の並び方が不規則なアモルファスは、規則性のある結晶に比べて熱の伝わり方が小さく、熱膨張率を低く抑えることができます。

また、球状フィラーには熱膨張率を下げるという以外にも、流動性を付与するという重要な性質があります。

アンダーフィル材は粘度が高いと全体に行きわたる前に途中で止まってしまうため、狭い隙間全体にきちんと行きわたる高い流動性が必要になります。

この点、球状シリカは角張った粉体に比べて粒子間の摩擦が少ないため、充填量を増やしても流動性を高く保つことができます。

ただし、フィラーの量が多すぎると、被着体との界面における樹脂の割合が相対的に減少して接着力が低下しやすくなるため注意が必要です。

硬化剤

エポキシ樹脂を硬化するためには、エポキシ基を持つ分子同士の間をつなぐ存在が必要であり、その役割を果たすのが硬化剤です。

硬化剤を使用することで分子同士が結合し、強固な三次元の網目構造を作ることができます。

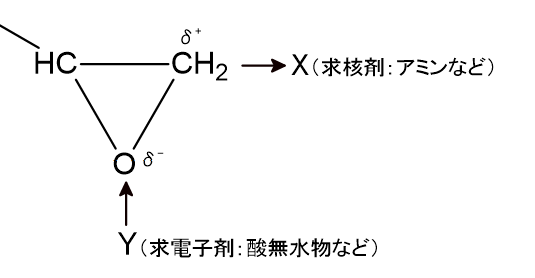

エポキシ樹脂の特徴として、アミンのような求核剤、酸無水物のような求電子剤の両方の硬化剤が使えるというメリットがあります。

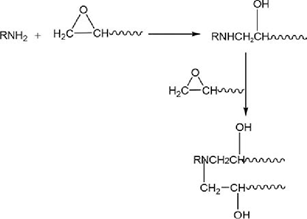

アミンは、窒素原子上に非共有電子対を持つため、この電子を他の原子に与えることで安定する電子供与性(求核性)であるため、エポキシ基の正に帯電している炭素原子と反応します。

アミン硬化剤が複数のエポキシ分子と反応して架橋することで、強固な網目構造が形成されます。

(画像引用元:https://www.researchgate.net/figure/Curing-reaction-of-epoxy-resin_fig6_303517892)

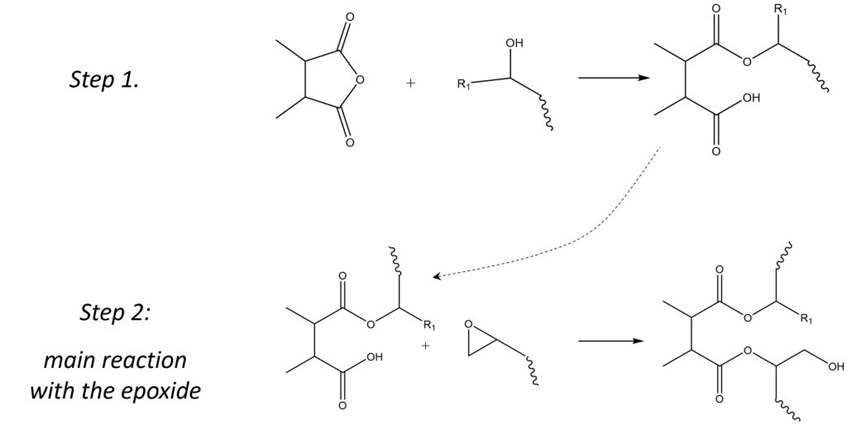

酸無水物は、2分子のカルボン酸が脱水縮合して生成する化合物で、代表例として無水フタル酸などがあります。

酸無水物単独ではエポキシ環を直接開環しにくいため、まずアルコールや微量水などの水酸基源と反応してカルボン酸を生成します。

生成されたカルボン酸は酸触媒として作用し、プロトンをエポキシ基の負に帯電している酸素に与えて環を活性化します(酸素のプロトン化により隣接炭素のδ+が増加)。

その後、酸無水物由来のカルボキシレートアニオン(–COO⁻)がこの炭素に求核攻撃して環を開きます。 この反応が分子間で繰り返されることで、三次元的な架橋構造が形成され、樹脂が硬化します。

(画像引用元:https://polymerinnovationblog.com/epoxy-curing-agents-anhydrides-long-pot-life-and-exceptional-properties/)

エポキシ樹脂には、硬化剤をあらかじめ樹脂と混ぜ合わせておく1液型と、使用直前に硬化剤と混ぜ合わせる2液型とがありますが、アンダーフィル材としては混合ムラや異物混入のリスクが少ない1液型が好まれます。

アンダーフィル材に求められる特性

以上の内容をまとめると、アンダーフィル材に求められる要素は以下のようにまとめられます。

①パッケージと配線基板、あるいはチップとパッケージ基板やインターポーザとの隙間に十分に浸透して硬化すること(高い濡れ性、低粘度)

②熱的応力、物理的応力に対して接続信頼性を維持できること

③電気特性(絶縁性等)が良好であること

④コスト面重視の場合、リペア性を有すること

アンダーフィル材のトラブルと信頼性試験

これまで説明してきたように、アンダーフィル材は封止部分に隙間なく充填され、過酷な環境下でもチップと基板との接続信頼性を保てるようにする必要があります。

したがって、その性能を確認するための試験が重要になります。

主なトラブル

まず、アンダーフィル材にはどのような不良が起こりやすいのかを見ていきましょう。

主なトラブルは、ボイドの発生、フィレット不足、クラック、界面破壊です。

ボイドの発生

アンダーフィル材が浸透する間に気泡を取り込んでそのまま固まってしまったり、粘度が高すぎて十分に浸透せずに隙間が残ってしまったりすると、その部分はボイドとして耐衝撃性を低下させてしまいます。

フィレット不足

理想的なアンダーフィルでは、端部がチップを抱き込んで丸みを帯びたような形状になります。これはフィレットと呼ばれています。

アンダーフィル材の充填不足によりフィレットが不十分な場合、チップをきちんと抱き込めず、基板との接着性が弱まる恐れがあります。

クラック

アンダーフィル材が硬すぎると熱で基板が膨張していった際にチップを割ってしまう恐れがありますが、脆くてもアンダーフィル自体が割れてしまいます。

また、アンダーフィル材の熱膨張率が高くても、膨張時にチップを押し上げてはんだが割れてしまいます。

界面破壊

アンダーフィル材の接着強度が低いとアンダーフィルと基板の間、あるいはアンダーフィルとチップの間の界面で剥離が生じてしまいます。

このような現象は界面破壊と呼ばれます。

信頼性試験

上記のようなトラブルが起きないために、事前の信頼性試験が重要になります。

主な試験項目について見ていきましょう。

浸透性試験

ボイドや充填不足を起こすことなくアンダーフィル材が十分に浸透するかどうかの試験です。

簡易的には、スライドガラスなどの平滑な2枚のガラス板を用意して、それらを一定の隙間を作って貼り合わせ、その隙間にアンダーフィル材を流し込んで流動性を確認します。

ただし、この方法は実際の材料を使っておらず再現性に劣るため、実装品の検査ではSAT(Scanning Acoustic Tomography)による非破壊検査を用いて、ボイド・クラック・剥離を直接確認することが推奨されます。

落下試験

物理的強度の試験としては、実装後のデバイスを一定の高さから落下させ、破損の有無を確認する落下試験が行われます。

ポータブル機器向け製品では必須であり、複数方向からの落下条件や繰り返し落下を行うことで耐衝撃性を評価します。

曲げ試験

垂直方向の機械荷重によって曲げを生じ、不良の有無を確認します。

通常は、下方向の2点から試料の両端を支え、中心となる1点で上方向からの垂直荷重をかける3点曲げという方法で行われます。

(画像引用元:https://www.instron.jp/ja/industry-solutions/electronics/microelectronics/bend-testing-of-printed-circuit-boards/)

温度サイクル・熱疲労試験

先述の通り、車載向け機器などは厳しい温度変化にさらされる場合があるため、そのような温度変化においても変形を起こさないようにする必要があります。

そのため、-50℃前後~125℃前後の温度変化を3000サイクル程度実施するサーマルサイクル試験により、不良がないことを確認します。

また、急激な温度変化を与えるサーマルショック試験によって、急な温度変化でも歪みが出ないことを確認します。

参考

- 半導体技術ロードマップ専門委員会「平成20年度報告 第8章 WG7 実装」

- 本多進「半導体素子の2D~3D実装技術動向と狙うべき方向」(エレクトロニクス実装学会誌、Vol.18、No.3、2015)

- 久保山俊史「アンダーフィル材 概論」(日本ゴム協会誌、第84巻、第10号、2011年)

- 名塚健「BGA・CSP実装用アンダーフィル剤」(スリーボンド・テクニカルニュース、平成12年7月号)

- 笛田・山田技術士事務所サイト「シリカの形状で変わる性能:球状・不定形・中空・多孔質を徹底比較」

コメントを残す